**DIGITAL INDUSTRIES SOFTWARE**

## Using AI for advances in test

Technology brief

#### **Executive summary**

This document summarizes the usage of AI in Tessent products from expert user automation to machine learning. We summarize capabilities available to you today and ongoing work on potential improvements embedding AI in our automation.

## Contents

| Tessent perspective on automation                 | 3 |

|---------------------------------------------------|---|

| ATPG Expert                                       | 4 |

| Automated debug                                   | 4 |

| Machine learning to find trends in scan fail data | 5 |

| DFT planning and tradeoff optimization            |   |

| with many variables                               | 6 |

| A new DFT architecture                            | 7 |

| Looking forward                                   | 8 |

| Layout pattern systematics                        | 8 |

| Training ATPG on circuit structures               | 8 |

| Knowledge access acceleration                     | 8 |

| References                                        | 8 |

### Tessent perspective on automation

The goal of electronic design automation (EDA) is to simplify the design tasks and enable greater capabilities using automation embedded within software tools.

Siemens EDA tools embed three types of AI within them as shown in Figure 1. Analytical AI solves problems algorithmically and creates more intuitive tools and processes. Predictive AI uses training and previous learnings to predict and improve results. Generative AI creates new insights and methods with self-learning.

Figure 1. Al solutions built with verifiability at their core.

"Tessent's charter is to provide highly automated solutions proven and tuned on real silicon prior to release." When using EDA tools, you want to be confident that the tools are effective and robust. This is a basic principle within Tessent and how we develop products.

At Tessent we have proven AI methods and machine learning technologies deployed. We continue to enhance other areas within our products with AI methods.

Users have better things to do with their time than to play with variables and adjust tool settings. The Tessent approach is to solve problems as much as possible algorithmically, so users don't need to worry about detailed tradeoffs. If the best result is to proceed with a certain sequence, adjust based on observed data and proceed, then it can be embedded algorithmically. Similarly, if a full interpretation of results requires additional tests and reports then those can be run and set up ahead of time. This is the type of automation is commonly embedded within the Tessent algorithms.

Additionally, a user needs to understand how a tool decision was made and have the ability to perform tradeoffs. Explainability of the results from algorithms has been a cornerstone of our approach. We empower users with both algorithms that optimize and then present the trade-offs that were made. If the user wants to explore other options, for instance prioritize one parameter, then they can adjust the operation sequence to accommodate their workflow.

There are cases where companies want to build their own special type of company-specific customized flows. This is made possible with the Tessent Platform environment. Within the Platform, the user has access to "introspect" data of which the tool is aware and may build custom scripts for their special needs. This gives the user the ability to create tool-level features, design rule checks and more, and register them as commands.

#### **ATPG Expert**

### Embed user knowledge and decision-making within the tools

Expert systems are a simple form of AI which mimics the knowledge and decisions of an expert user. A few expert systems were embedded within Tessent Automatic Test Pattern Generation (ATPG) to simplify the ATPG process.

"ATPG Expert" was built to simplify the task of analyzing the design to determine the best parameters to set for an ATPG run. The goal is to optimize coverage and pattern count automatically.

Previously, these types of decisions would have varying results depending on the user's knowledge. To make work easier, ATPG Expert decides on the most appropriate settings based on design characteristics. This includes:

- Which clocks to pulse

- Abort limits: based on design complexity how many "tries" before aborting on a targeted fault

- Contention checks

- Sequential depth: how many pulses to apply after shifting is complete to load non-scan cells prior to capture

- ... and more

Furthermore, a user can just set the parameters and then start a session creating patterns. The ATPG Expert capability being embedded in the software algorithms can view the results during an ATPG run and adjust mid-run. Therefore, ATPG Expert can adapt during the session and adjust to re-optimized parameters based on the progress it observed.

These types of algorithmic adjustments, which are beyond human capability, are referred to by Tessent as "analytical AI."

#### Automated debug

A second expert system is sometimes referred to as "fault grouping." Many times after running ATPG, you might need to run a few experiments to debug missing coverage. Much of the data from these types of experiments are now embedded in the ATPG run. Once the run is complete, there is a summary of various types of fault categories and coverage impact. There is no need for additional tests.

Some of the types of information automatically provided are:

- Grouping of AU faults: AU faults are determined to be ATPG Untestable. These are now further broken down into specific categories such as in IJTAG logic (AU.IJTAG), OCC logic (AU.OCC), and more

- Sequential fault depth: a summary of % of faults not detected because they need a higher sequential nonscan cycle depth

- Constrained pins: a breakdown of total loss of coverage due to each constrained primary input pin

- Constrained cell: a breakdown of internal registers that are learned to initialize to a static state and stay there and how much they impact coverage

- Coverage loss by clock domain: this is also shown in the Tessent Visualizer GUI application to give a simple hierarchical view of coverage loss sorted by capture clocks

|                                        |          |                       |                                                          |                                 | Cell Lib  | rary Browser         | -1 | essent Visual            | lizer (o | n tes  | ssentshare | ddev11)                 |  |

|----------------------------------------|----------|-----------------------|----------------------------------------------------------|---------------------------------|-----------|----------------------|----|--------------------------|----------|--------|------------|-------------------------|--|

| Open Search Macros                     | Settings |                       |                                                          |                                 |           |                      |    |                          |          |        |            |                         |  |

| 📶 Instance Browser 🕱 📴 DRC Browser 🕱 🗵 |          |                       | Transcript                                               | Transcript 🕱 🔡 Flat Schematic 🕱 |           |                      |    | 🔳 Cell Library Browser 🕱 |          |        |            |                         |  |

| 👿 🔜 🗔 🛛 🖏                              |          |                       |                                                          |                                 |           |                      |    | 42                       | 0        |        |            | 6                       |  |

| Module name                            |          | Number o<br>instances | f Total faults                                           | Avg Test<br>Coverage            |           | Max Test<br>Coverage |    | TC Loss                  | -        | Filter |            |                         |  |

| Filter                                 |          | Filter                | Filter                                                   | Filter                          | 1         | ilter                | 1  | Filter                   |          |        |            |                         |  |

| nck_dff                                |          | 2                     | 9 1                                                      | 10                              | 0.00%     | 100.00%              | T) | 0.00%                    |          |        |            |                         |  |

| and02                                  |          | 8                     | 0 7                                                      |                                 | 0.00%     | 100.00%              |    | 0.00%                    |          |        |            |                         |  |

| oai22                                  |          | 3                     | 5 1                                                      |                                 | 0.00%     |                      |    | 0.00%                    |          |        |            |                         |  |

| and03                                  |          | 1                     | 1 1                                                      |                                 |           |                      |    | 0.00%                    |          |        |            |                         |  |

| oai32                                  |          | 26                    | 5 29                                                     |                                 | 6.00%     |                      |    | 0.21%                    |          |        |            |                         |  |

| nand03                                 |          | 11                    | 2 1                                                      | 10                              | 0.00%     |                      |    | 0.00%                    |          |        |            |                         |  |

| sffr                                   |          | 84                    | 4 13                                                     |                                 | 0.00%     |                      |    | 0.00%                    |          |        |            |                         |  |

| oai322                                 |          |                       | 7                                                        |                                 | 1 100.00% |                      | 1  | 0.00%                    |          |        |            |                         |  |

| Tree view                              | Type ,   | , Instance nam        | e Module                                                 | Module name                     |           | s Test Covera        | ge | TC Loss                  | AU.SEQ   |        | AU.UNC     | Total DRC<br>violations |  |

| <top></top>                            | Filter   | Filter                | Filter                                                   |                                 | Filter    | Filter               |    | Filter                   | Filter   |        | Filter     | Filter                  |  |

| • U_0                                  | Instance | U_0                   | RSDecoder                                                | RSDecoder_0                     |           | 8 100.00%            | T) | 0.00%                    |          | 0      | 0          | 10                      |  |

| ↓ U_1                                  | Instance | U_1                   | RSDecoder_6<br>RSDecoder_5<br>RSDecoder_4<br>RSDecoder_3 |                                 | 44        | 8 100.00%            |    |                          |          | 0      | 0          | 9                       |  |

| ↓ U_2 ↓ U_3                            | Instance | U_2                   |                                                          |                                 | 34        |                      |    | 0.00%                    |          | 0      | 0          | 10                      |  |

| ↓ U_6                                  | Instance | ce U_6                |                                                          |                                 | 33        |                      |    | 13.03%                   |          | 143    | 115        | 847                     |  |

| > U 7                                  | Instance |                       |                                                          |                                 | 31        |                      |    | 0.00%                    |          | 0      | 0          | 11                      |  |

| ▶ U_8                                  | Instance | U_7                   | RSDecoder                                                |                                 | 36        |                      |    | 0.00%                    |          | 0      | 0          |                         |  |

|                                        | Instance | 11.8                  | RSDecoder                                                | 1                               | 35        | 100.00%              | 1  | 0.00%                    | 1        | 0      | 0          | 12                      |  |

Figure 2. Tessent Visualizer can summarize coverage loss due to library models, capture clocks, and as shown hierarchical instances and modules.

#### Machine learning to find trends in scan fail data AI can find yield limiters that are hidden from humans.

Semiconductor production yield has a direct impact on a product's profitability. It is vitally important to quickly get the yield high enough for volume production and to find opportunities to improve yield when in volume production. Al's strength is combining more data, building up higher level relationships and uncovering additional yield limiters.

Expertise-based AI was first employed about 15 years ago to improve scan diagnosis. This type of probability-based diagnosis grouped faults based on known/expert characteristics. This filters many candidates into the most likely suspects. This was found to result in more than 5x fewer suspects in a diagnosis call-out.

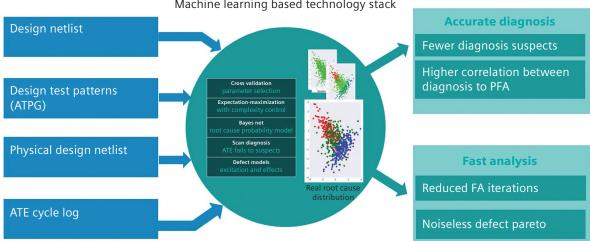

Semiconductor production can be in the millions and has lots of scan fail data available. The analysis of a large number of scan fail data from volume diagnosis for yield limiters lends itself into machine learning to find trends that are hard for a human to recognize. Tessent employs unsupervised machinelearning (Brady Benware, 2012) but with some limited guidance. The results were a few notable

capabilities that improved identification accuracy and resolution of yield limiters. Some examples of this form of machine-learning are:

- Profiling-based chain diagnosis: This method was implemented in Tessent tools more than 10 years ago. It improved diagnosis accuracy by 2x and improved resolution by >2x fewer suspects. The same method was applied to logic diagnosis as well

- Root cause deconvolution (RCD): First published about 10 years ago. RCD hides the noise from the likely suspects (Brady Benware, 2012). It has been proven in Pareto charts across more than 10 nodes, including down to 3 nm. One recent case study of RCD in production in 2023 but not published at the time of this paper is a production yield improvement of 2.5% in an already high yield product

- Population-based statistical diagnosis: Improving beyond RCD to further weed out suspects are not important. An electrical fault isolation (EFI) case published in ISTFA 2021 described avoiding EFI on 2.4x additional failing die, which resulted in more than \$1 million dollars of savings a month.

#### **Diagnosis driven yield analysis**

Machine learning based technology stack

Figure 3. The application of machine learning to improve yield.

## DFT planning and tradeoff optimization with many variables

# One of the best solutions to a complex problem is to change the problem so that it is simpler.

When designing a full SoC there are many tradeoffs related to the DFT architecture. A top-level DFT architecture traditionally needs to balance and optimize the following parameters:

- Within each core

- # input scan channels feeding embedded compression

- # output scan channels from embedded compression

- Size of the pattern set generated for the core

- Length of the scan chains in the core

- Number of scan chains based on available scan channels

- At the top level

- # of IO pins available to provide scan data

- Power constraints from running multiple cores in parallel

- A test access management (TAM) mechanism to test groups of cores. The simplest form is a large mux structure from core output channels to chip IO pins controlled by a test mode setting

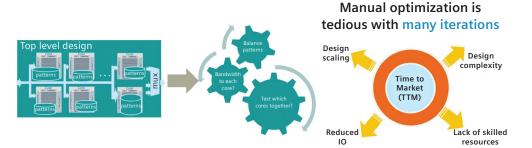

It often takes many iterations as the core designs evolve to produce an effective DFT architecture. Some users state that they required hundreds of iterations when planning their DFT architecture. It is very difficult to select the best set of cores to test in parallel and balance how many of the available IOs to route to each; some cores may have different scan chain lengths. This gets complicated because the pattern size varies between cores which impacts how many scan channels (bandwidth) to apply to each core. As the core designs evolve, their scan channel requirements may change; a pattern set's size may be different than expected necessitating further iterations. Given a design with 100s of cores, you would need to potentially balance 1000 variables, many of which change during the design development.

#### DFT architecture design has a direct impact on time to market and suffers from design and resource trends.

The DFT architecture challenge is harder with newer, more complex designs. These designs continue to scale in total numbers of cores, gate count and numbers of identical cores. At the same time, often the number of IO pins available for test is reducing and the availability of skilled DFT engineers is reducing. This challenge is summarized in the figure 4 below. If you wait until all the core designs and patterns are complete, then there are many variables that must be balanced and the core DFT designs reworked to balance the bandwidth available from the IO.

Figure 4. Tradeoffs necessary when designing an SoC complicated by design and resource trends which further impact time to market.

In addition to the trouble balancing all the variables to design test modes and allocation IO pin bandwidth, the traditional solution is usually static. A DFT architecture often doesn't have a lot of flexibility to adjust for issues such as additional patterns found to be necessary, Engineering Change Orders (ECOs), adjustments to cores tested in parallel, or other late changes or observations.

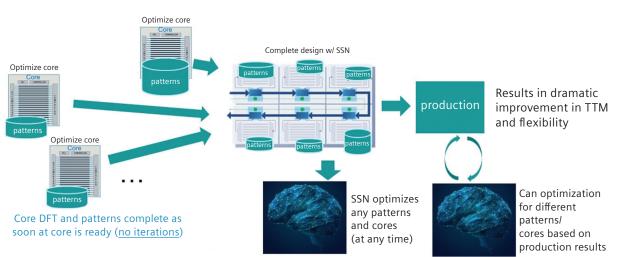

#### A new DFT architecture Change the problem so these many variables don't exist

Tessent Streaming Scan Network (SSN) provides a new type of DFT architecture that removes the difficult tradeoffs mentioned above. SSN uses a packetized data delivery mechanism for scan data. Any size SSN bus can be used to deliver data to any size scan channels at various cores. Thus, there is no need to iterate on balancing IO to cores, or even to have a top-level test access mechanism (TAM).

A huge benefit from SSN is that core DFT insertion and pattern generation can be completed when that core is ready. There is no need to wait for other cores and re-balance and adjust the core. This is a dramatic improvement in DFT architecture time to market. All the variables that traditionally needed to be balanced are now not a factor. Some well-known industry leaders have reported as much as 10x productivity improvement when utilizing SSN (Côté, et al., 2020). When the final design is complete, the user can decide which patterns to apply to which cores in parallel. At that point, SSN algorithms automatically balance the packet data for each core such that the tests of the groups of cores all complete around the same time. This optimization can happen at any time and can be changed at any time. It is another form of "analytical Al" since the tool performs the optimizations and can be adapted at any point.

An additional benefit of SSN and using packetized scan delivery mechanism is that each core operates independently when the packet data is delivered. Clock generation exists at each core's SSN interface to perform clock strobes for shift and capture operations. This means that there is no longer a need to close timing for scan en or shift clocks throughout the entire design. Timing closure is greatly simplified. Even more significant is the impact on power during test. Cores shift and capture independently so the power during scan test is greatly reduced. This is even true for identical cores since their input data is shared but serially transferred to each identical core. Cores will shift when their packet data is available; it doesn't need to wait or align with any other core.

Figure 5. SSN removes the need to trade off and optimize core scan channels/patterns with the embedding and IO pins available.

## Looking forward

## Training DFT tools to learn and guide users.

#### Layout pattern systematics

Tessent has partnered with PDF Solutions to find layout patterns that are prone to fail (Cheng, et al., 2017). This big data analysis presents an opportunity to improve yield by an additional 1-3%.

#### **Training ATPG on circuit structures**

Machine learning has a potential to perform optimizations on ATPG by learning certain characteristics about a design (Joe, Mukherjee, Pomeranz, & Rajski, 2022). If there is a similar design or the design undergoes an ECO, the tools can take advantage of what specifically has changed compared to what was learned in the baseline. A full ATPG run is not required.

#### **Knowledge access acceleration**

There is a broad opportunity to help automate or guide the user to effective results quickly. This is especially important for businesses that have trouble finding resources skilled in DFT. Using a co-pilot flow/methodology guidance can be helpful for new and experienced users. Instead of having to know all the details, the tool could assess where the design is in the DFT insertion or pattern generation process and guide them forward. Many of the lower-level detailed operations can be automated based on higher level intent commands.

Another opportunity is to perform experiments to find the optimal configuration for DFT, compression configuration or ATPG for a particular design. Our customers have already experienced up to a 5x pattern application time improvement using a prototype compression advisor utility.

In summary, test tool technology has tried to simplify and automate design tasks algorithmically. Some features you have access to include automation to adapt during the sessions. In some cases, the size of the data is beyond simple algorithmic solutions such as with yield learning and the usage of machine learning. Going forward, we are aggressively working on AI technologies to provide additional benefits for your DFT and design work.

#### References

- Brady Benware, C. S. "Determining a failure root cause distribution from a population of layout-aware scan diagnosis results", *IEEE Design & Test of Computers*, 2012.

- Cheng, W.-T., Klingenberg, R., Benware, B., Yang, W., Sharma, M., Eide, G., ... Chittora, A. "Al's strength is combining more data, building up higher level relationships and uncovering additional yield limiters", 2017 IEEE 26<sup>th</sup> Asian Test Symposium (ATS) (pp. 27-30), IEEE, 2017.

- Côté, J.-F., Kassab, M., Janiszewski, W., Rodrigues, R., Meier, R., Kaczmarek, B., ... Pant, P. "Streaming Scan Network (SSN): An efficient packetized data network for testing of complex SoCs", 2020 IEEE International Test Conference (ITC), IEEE, 2020.

- D. Trock, R. F. "Recursive hierarchical DFT methodology with multi-level clock control and scan pattern retargeting", Design, Automation & Test in Europe Conference & Exhibition (DATE), IEEE, 2016.

- Joe, J., Mukherjee, N., Pomeranz, I., & Rajski, J. "Test generation for an iterative design flow with RTL changes", *IEEE International Test Conference (ITC)* (pp. 305-313), Anaheim: IEEE, 2022.

- Ron Press, F. A. "The application of neural network technology to built-in test false alarm filtering", *American Institute* of *Aeronautics and Astronautics, Inc*, Aerospace Research Center, 1993.

#### **Siemens Digital Industries Software**

Americas: 1 800 498 5351 EMEA: 00 800 70002222 Asia-Pacific: 001 800 03061910 For additional numbers, click <u>here</u>. Siemens Digital Industries Software helps organizations of all sizes digitally transform using software, hardware and services from the Siemens Xcelerator business platform. Siemens' software and the comprehensive digital twin enable companies to optimize their design, engineering and manufacturing processes to turn today's ideas into the sustainable products of the future. From chips to entire systems, from product to process, across all industries, <u>Siemens Digital Industries Software</u> – Accelerating transformation.

#### siemens.com/software

$\circledast$  2024 Siemens. A list of relevant Siemens trademarks can be found <u>here</u>. Other trademarks belong to their respective owners.