Pat-Man

Enhance semiconductor reliability

Facing strict quality demands from the automotive industry, semiconductor companies are increasingly applying Part Average Testing (PAT) to enhance reliability. PAT identifies and removes “outlier” parts that pass standard tests but exhibit abnormal characteristics, reducing long-term quality and reliability issues. By statistically analyzing multiple devices and adjusting pass/fail limits, PAT proactively identifies these problematic parts for exclusion, ensuring only the most reliable components reach production shipments.

Part Average Testing ( PAT ) as detailed in the Automotive Electronics Council AEC-Q001-Rev C specifications only covers DPM techniques for normal (Gaussian) distributions. However, many distributions do not fall into the Gaussian category and require adapted PAT outlier detection methods to avoid excessive yield loss or incorrect outlier detection.

PAT-Man is a comprehensive solution for Part Average Testing (PAT), empowering manufacturers in the identification and removal of outliers, defects per million (DPM) reduction, and enhancement of overall product reliability.

PAT-Man™ seamlessly manages the entire DPM reduction process, from initial wafer lot characterization to final test yield monitoring. Based on proven architecture and intuitive user interface, PAT-Man™ integrates easily with your existing production test environment and provides the fastest and most cost-effective solution for DPM reduction in the industry.

Pat-Man Lite

Pat-Man is a scalable solution for any engineer, whether at a start-up or a large company.

For those with smaller production volumes and who need the power and flexibility of Pat-Man’s recipe generator but may not currently need the automation engine of the full Pat-Man solution, ask us about Pat-Man Lite!

PAT-MAN APPLICATIONS

PAT-Man seamlessly integrates with your existing production test environment, providing a powerful toolset for managing the entire DPM reduction process, from initial wafer lot characterization to final test yield monitoring.

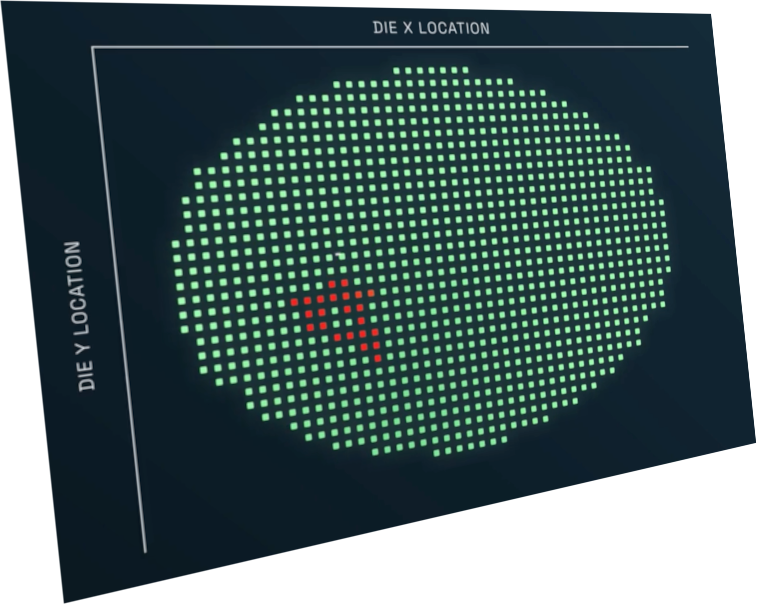

- Wafer sort: Post-processing step that covers parametric PAT, geographic PAT (good die in bad neighborhood), reticle PAT, and combinations of the above.

- Final Test: Real-time process on the tester, which covers parametric PAT, trend monitoring, yield monitoring, and alarm/reporting notifications.

- Static PAT limits: Support for Automotive Electronics Council AEC-Q001 Rev C and JEDEC specifications

- Dynamic PAT limit: Auto-adaptive algorithms for Gaussian distributions as well as non-Gaussian for minimized yield loss.

KEY BENEFITS

- Significantly reduce quality and reliability issues and associated costs

- Rapidly identify process shifts and implement corrective actions

- Enhancecommunication and collaboration across the supplu chain

- Improve the reliability of products and manufacturing processes